## **Sequential Circuit Synthesis**

## Y-0016/003D and 001D board (given in next page)

Verfiy the truth table of JK, D and T type Flipflops.

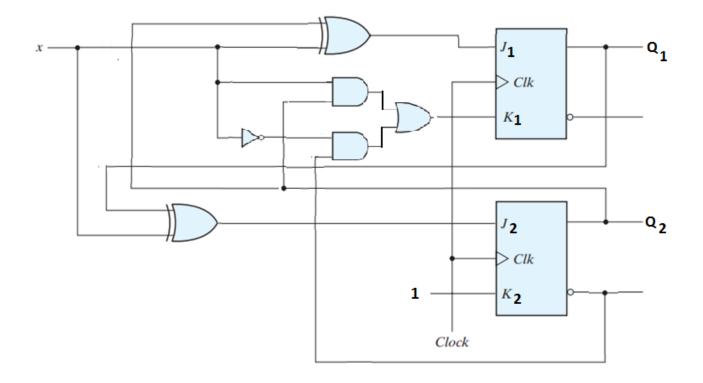

1. For the circuit given below formulate the truth table and the state diagram. Here, X represents the input, and Q represents the outputs (the states) of the JK type flip flops. Then, implement the circuit and verify your results.

## Logic Lab – Exp #7

|      | SR Flip | -flop | D Flip-flop |      |        |    |

|------|---------|-------|-------------|------|--------|----|

| Q(t) | Q(t+1)  | S     | R           | Q(t) | Q(t+1) | DR |

| 0    | 0       | 0     | X           | 0    | 0      | 0  |

| 0    | 1       | 1     | 0           | 0    | 1      | 1  |

| 1    | 0       | 0     | 1           | 1    | 0      | 0  |

| 1    | 1       | X     | 0           | 1    | 1      | 1  |

|      | JK flip | -flop | T flip-flop |      |        |    |

|------|---------|-------|-------------|------|--------|----|

| Q(t) | Q(t+1)  | J     | K           | Q(t) | Q(t+1) | DR |

| 0    | 0       | 0     | x           | 0    | 0      | 0  |

| 0    | 1       | 1     | x           | 0    | 1      | 1  |

| 1    | 0       | x     | 1           | 1    | 0      | 1  |

| 1    | 1       | x     | 0           | 1    | 1      | 0  |