## **Sequential Circuit Synthesis**

## Y-0016/004D and 001/2D board (given in next page)

Verfiy JK flip flops with the truth table using Y-0016/004D board for each FF.

## **Design Example**

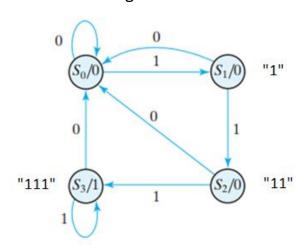

Suppose we wish to design a circuit that detects a sequence of three or more consecutive 1's in a string of bits coming through an input line. The input is a serial bit stream.

State diagram

| Present<br>State |   | Input | Next<br>State |   | Output |  |

|------------------|---|-------|---------------|---|--------|--|

| A                | В | X     | A             | В | у      |  |

| 0                | 0 | 0     | 0             | 0 | 0      |  |

| 0                | 0 | 1     | 0             | 1 | 0      |  |

| 0                | 1 | 0     | 0             | 0 | 0      |  |

| 0                | 1 | 1     | 1             | 0 | 0      |  |

| 1                | 0 | 0     | 0             | 0 | 0      |  |

| 1                | 0 | 1     | 1             | 1 | 0      |  |

| 1                | 1 | 0     | 0             | 0 | 1      |  |

| 1                | 1 | 1     | 1             | 1 | 1      |  |

Using JK flipflop and its excitation table:

| Q(t) | Q(t+1) | J | K |  |

|------|--------|---|---|--|

| 0    | 0      | 0 | X |  |

| 0    | 1      | 1 | X |  |

| 1    | 0      | X | 1 |  |

| 1    | 1      | X | 0 |  |

(a) JK Flip-Flop

State Table and JK Flip-Flop Inputs

| Present<br>State |   | Input | Next<br>State |   | Flip-Flop Inputs |                |                |                |

|------------------|---|-------|---------------|---|------------------|----------------|----------------|----------------|

| A                | В | x     | A             | В | JA               | K <sub>A</sub> | J <sub>B</sub> | K <sub>B</sub> |

| 0                | 0 | 0     | 0             | 0 | 0                | Χ              | 0              | Х              |

| 0                | 0 | 1     | 0             | 1 | 0                | X              | 1              | Χ              |

| 0                | 1 | 0     | 0             | 0 | 0                | Χ              | Χ              | 1              |

| 0                | 1 | 1     | 1             | 0 | 1                | Χ              | X              | 1              |

| 1                | 0 | 0     | 0             | 0 | Χ                | 1              | 0              | X              |

| 1                | 0 | 1     | 1             | 1 | X                | 0              | 1              | X              |

| 1                | 1 | 0     | 0             | 0 | X                | 1              | X              | 1              |

| 1                | 1 | 1     | 1             | 1 | X                | 0              | Χ              | 0              |

After filling J, K in the table, Karnough map will be used to simplfy and to find inputs of JK flipflops.

- **1.** A stream of **0's** and **1's** coming from a serial transmission channel. A sequential circuit will be designed that detects **011** sequence coming through this input line.

- a. Draw the state diagram.

- b. Fill in the state table using JK flipflops

- c. Simplify the JKs in Karnough and find their input definitions

- d. Implement the circuit using Y-0016/004D board and other necessary gate boards.