# **ELECTRONICS LABORATORY**

# **PART 7 EXPERIMENTS**

Assoc. Prof. Serhan Yarkan

**ISTANBUL COMMERCE UNIVERSITY**

### Contents

| EXPERIMENT: 7.1                             | 2 |

|---------------------------------------------|---|

| EXAMINATION OF INTEGRATED SOUND AMPLIFIER   | 2 |

| EXPERIMENT 7.2                              | 4 |

| EXAMINATION OF JFET'S INPUT CHARACTERISTICS | 4 |

| EXPERIMENT 7.3                              | 7 |

| EXAMINATION OF JFET                         | 7 |

| EXPERIMENT 7.4                              | 8 |

| EXAMINATION OF JFET                         | 8 |

## **EXPERIMENT 7.1** EXAMINATION OF JFET'S INPUT CHARACTERISTICS

#### **EXPERIMENTAL PROCEDURE:**

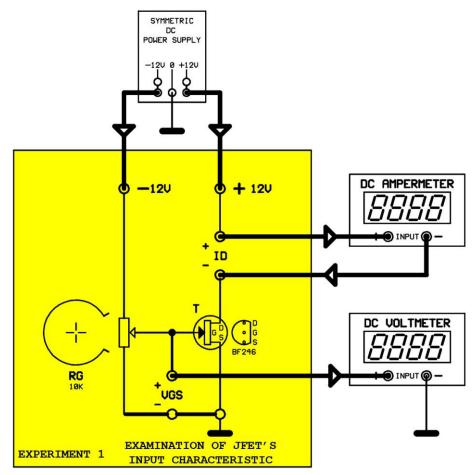

Plug the Y-0016/012 module. Make the circuit connections as in Figure 7.1.

Figure 7.1

**1-** Type the VGS voltage to the table at Figure 7.2 with the help of RG potentiometer. Also type the ID values for each step.

| $V_{DS} = 12V CONSTANT$ |               |  |  |  |  |  |  |

|-------------------------|---------------|--|--|--|--|--|--|

| $V_{GS}$                | $I_D$         |  |  |  |  |  |  |

| (VOLT)                  | ( <i>m</i> A) |  |  |  |  |  |  |

| 0.0                     |               |  |  |  |  |  |  |

| -0.5                    |               |  |  |  |  |  |  |

| -1.0                    |               |  |  |  |  |  |  |

| -1.5                    |               |  |  |  |  |  |  |

| -2.0                    |               |  |  |  |  |  |  |

| -2.5                    |               |  |  |  |  |  |  |

| -3.0                    |               |  |  |  |  |  |  |

| -3.5                    |               |  |  |  |  |  |  |

| -4.0                    |               |  |  |  |  |  |  |

| Figure 7.2              |               |  |  |  |  |  |  |

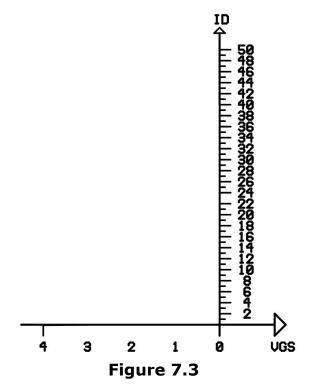

2- Draw the VGS/ID curve using the values in Figure 7.2.

**3-** When the **VGS=**-3.5V or at a smaller value ID="0". What is the name for this value of VGS?

## **EXPERIMENT: 7.2** EXAMINATION OF JFET'S OUTPUT CHARCTERISTICS

### **EXPERIMENTAL PROCEDURE:**

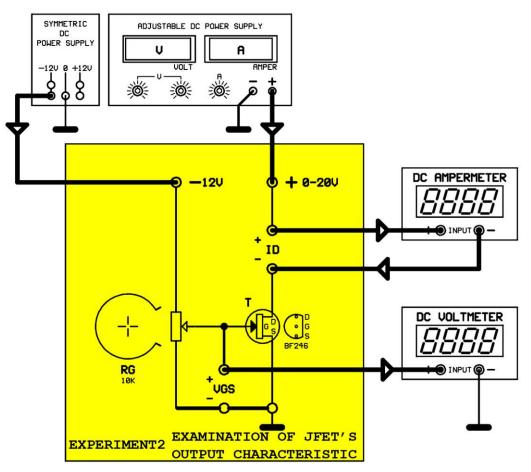

Plug the Y-0016/012 module. Before making the connections, adjust the output voltage of power supply to " $\mathbf{0}$ " by rotating voltage potentiometers to left. And adjust the gate voltage to " $\mathbf{0}$ " by rotating the "**RG**" potentiometer to left.

Make the circuit connections as in Figure 7.4 and apply energy to circuit.

Figure 7.4

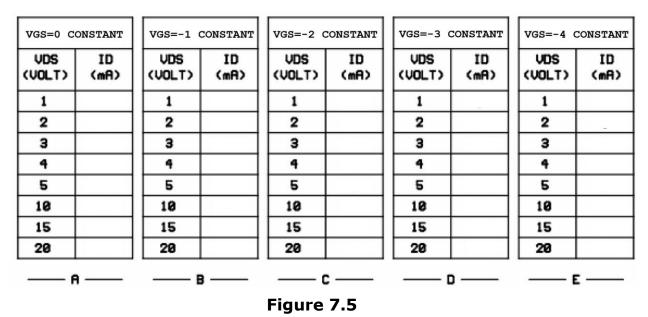

**1-** Set **VGS**=0 using "**RG**" potentiometer. Adjust the power supply voltage to the VDS voltage values in Figure 7.5 and make sure that **VGS=0** at each step. Type the ID values at each step to section "**A**".

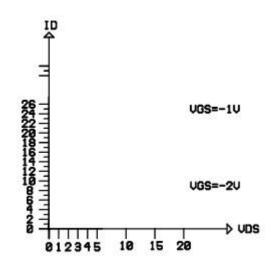

2- Draw change graphics between VDS/ID axes for each VGS voltage value.

Figure 7.6

$\ensuremath{\textbf{3-}}$  ID is constant even if the VDS is increased. What is the name for this value of ID?

**4-** Adjust the VGS voltage to-1V, -2V, -3V, -4V, respectively. Adjust the VDS voltage to the values in Figure 7.11 and type each ID value next to each VDS value.

| VGS=0 CONSTANT |            | VGS=-1 CONSTANT |            | VGS=-2 CONSTANT |             | VGS=-3 CONSTANT |            | VGS=-4 CONSTANT |            |  |

|----------------|------------|-----------------|------------|-----------------|-------------|-----------------|------------|-----------------|------------|--|

| VDS<br>(VOLT)  | ID<br>(mA) | VDS<br>(VOLT)   | ID<br>(mA) | VDS<br>(VOLT)   | ID<br>(mfi) | VDS<br>(VOLT)   | ID<br>(mR) | VDS<br>(VOLT)   | ID<br>(mA) |  |

| 1              |            | 1               |            | 1               |             | 1               |            | 1               |            |  |

| 2              |            | 2               |            | 2               |             | 2               |            | 2               | -          |  |

| 3              |            | 3               |            | 3               |             | 3               |            | 3               |            |  |

| 4              |            | 4               |            | 4               |             | 4               |            | 4               |            |  |

| 5              |            | 5               |            | 5               | _           | 5               |            | 5               |            |  |

| 10             |            | 10              |            | 10              |             | 10              |            | 10              |            |  |

| 15             |            | 15              |            | 15              |             | 15              |            | 15              |            |  |

| 20             |            | 20              |            | 20              |             | 20              |            | 20              |            |  |

| BCDE           |            |                 |            |                 |             |                 |            |                 |            |  |

| Figure 7.7     |            |                 |            |                 |             |                 |            |                 |            |  |

**5-** Draw change graphics between VDS/ID axes for each VGS voltage value.

Figure 7.8

6- What is the name for these graphics?

**7-** Write the effect of gate bias to drain current.

8- Write the effect of VDS voltage to drain current.

## EXPERIMENT: 7.3 EXAMINATION OF JFET

#### **EXPERIMENTAL PROCEDURE:**

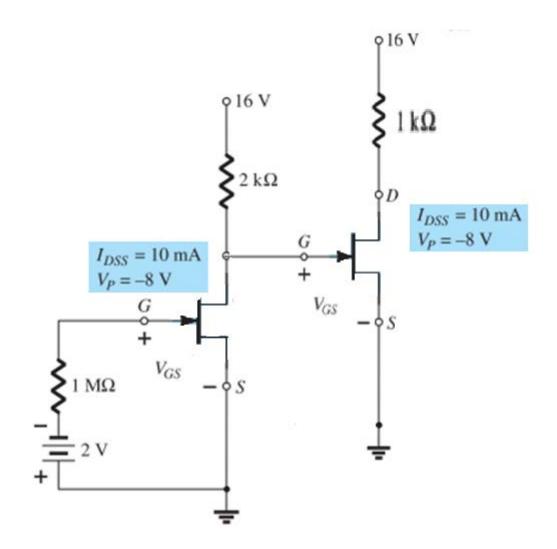

Make the circuit connection and apply energy to circuit. You can use the same JFET that you used for previous experiment.

- 1 Find the VGS1, ID1, VDS1, VGS2, ID2 and VDS2.

- 2 Plot the characterictics curve.

## EXPERIMENT: 7.4 EXAMINATION OF JFET

#### EXPERIMENTAL PROCEDURE:

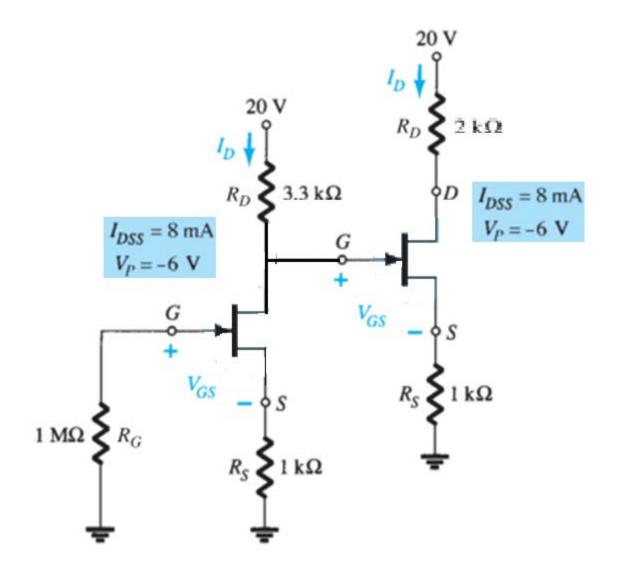

Make the circuit connection and apply energy to circuit. You can use the same JFET that you used for previous experiment.

- 1 Find the VGS1, ID1, VDS1, VGS2, ID2 and VDS2.

- 2 Plot the characterictics curve.